BMWi-Förderung

Im Rahmen des Förderprogramms „Signo-Verwertungsförderung-Weiterentwicklung“ wurde vom BMWi der Bau von Prototypen zur Demonstration patentgeschützter Verfahren der neuartigen Sicherheitstechnologie in 5D gefördert.

Das Vorhaben „Demonstrator-Echtzeitfähige dynamische permutierte Zufallsverschlüsselung“, Förderkennzeichen 03VWP0044, wurde an der Fakultät Elektrotechnik der Hochschule Schmalkalden von September 2010 bis Februar 2011 durch das Schmalkalder Kompetenzteam für Informationssicherheit in 5D unter Leitung von Prof. Dr. Werner Rozek durchgeführt.

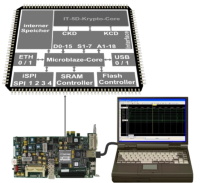

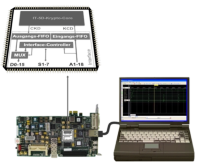

Ziel der Förderung war die Entwicklung eines vorwettbewerblichen Prototyps zur Demonstration der Funktionsweisen der neuartigen One-Time-Pad-Verschlüsselungsverfahren und deren FPGA-Umsetzbarkeit. Im Ergebnis dieser Förderung entstanden ein funktionsfähiger FPGA mit Secure 5D-Core, ein weiterer FPGA "IT5DRo3" mit Secure 5D-Core und Mikroblaze-Core sowie der SSR-Zufalls-Generator und ein Transparentes Security Gateway (TSG), das eine Softwarevariante der neuartigen OTP-Verschlüsselungsverfahren beinhaltete.

| |

weiterlesen...